4 �� 7 ����Ϣ������֪�R�a(ch��n)��(qu��n)����Ϣ�@ʾ���A�鼼�g(sh��)����˾ 3 �� 18 �չ�����һ����顰���M(j��n)��߉�T�·��Ӌ���·��оƬ�Լ�����O(sh��)�䡱�Č��������_̖�� CN119652311A����Ո���ڞ� 2023 �� 9 �� 18 �ա�

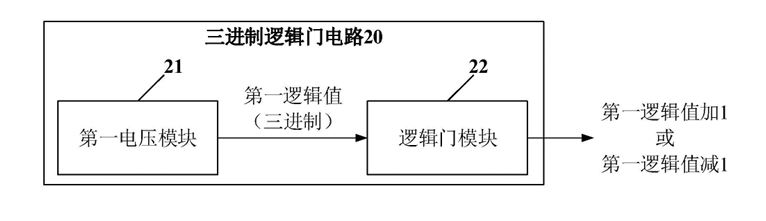

����ժҪ�@ʾ������Ո?zh��)ṩһ�N���M(j��n)��߉�T�·��Ӌ���·��оƬ�Լ�����O(sh��)�䣬����Ո?zh��)ṩ�����M(j��n)��߉�T�·���Ԍ�(sh��)�F(xi��n)ݔ��߉ֵ�ļ� 1���p 1������ԓ���M(j��n)��߉�T�·��������ֵ߉�� 27 �N��׃������(sh��)����ԓ���M(j��n)��߉�T�·��(y��ng)�������M(j��n)��߉�·�У����Ԍ�(sh��)�F(xi��n)�������M(j��n)��߉�·�ĽY(ji��)��(g��u)��Ŀ�ģ����Ԝp�����M(j��n)��߉�·�еľ��w�ܔ�(sh��)�����������M(j��n)��߉�·�Ĺ��ģ��Լ�������M(j��n)��߉�·��Ӌ��Ч����

IT֮�Ҹ������ļ��������g(sh��)��Ϣ��

�S����(sh��)��(j��)�r���ĵ�����̎������Ĕ�(sh��)��(j��)��Ҫ��оƬ���и��ߵ�Ӌ�����ܡ�Ŀǰͨ�^���εؿsС���w�ܵijߴ�����оƬ��Ӌ������׃�ø������y�������Ҫͨ�^�O(sh��)�ô�Ҏ(gu��)ģ�ļ����·���_(d��)�����оƬ��Ӌ�����ܵ�Ŀ�ģ����Ǵ�Ҏ(gu��)ģ�ļ����·���������߹����Լ���(li��n)��(f��)�s�ȡ�

���M(j��n)��߉��������ֵ߉�������Ϣ�ܶȣ����M(j��n)��߉�܉�Խ���M(j��n)��߉��Ӌ�����ܣ�������M(j��n)��߉�·��Ӌ�����ܸ��ڶ��M(j��n)��߉�·��Ӌ�����������M(j��n)��߉�T�·�ǘ�(g��u)�����M(j��n)��߉�·�Ļ��A(ch��)��Ԫ��������M(j��n)��߉�T�·���O(sh��)Ӌ���P(gu��n)��Ҫ��